# Using Hierarchical Scheduling to Support Soft Real-Time Applications in General-Purpose Operating Systems

A Dissertation

Presented to

the faculty of the School of Engineering and Applied Science

University of Virginia

In Partial Fulfillment

of the requirements for the Degree

Doctor of Philosophy

Computer Science

by

John D. Regehr

May 2001

© Copyright by

John D. Regehr

All rights reserved

May 2001

# Approvals

This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

| Doctor                      | of Philosophy                    |

|-----------------------------|----------------------------------|

| Comp                        | outer Science                    |

| _                           |                                  |

|                             |                                  |

|                             |                                  |

| John                        | D. Regehr                        |

|                             |                                  |

|                             |                                  |

| A                           | pproved:                         |

|                             |                                  |

|                             | -                                |

| John A. Stankovic (Advisor) | Paul F. Reynolds (Chair)         |

|                             | <b>,</b> , ,                     |

|                             |                                  |

| Midwal D. James             |                                  |

| Michael B. Jones            | Marty A. Humphrey                |

|                             |                                  |

|                             | <del>-</del>                     |

| Sang H. Son                 | Ronald D. Williams               |

|                             |                                  |

| Accepted by the School of   | Engineering and Applied Science: |

|                             |                                  |

|                             |                                  |

|                             |                                  |

| Richard W                   | V. Miksad (Dean)                 |

|                             |                                  |

May 2001

### **Abstract**

The CPU schedulers in general-purpose operating systems are designed to provide fast response time for interactive applications and high throughput for batch applications. The heuristics used to achieve these goals do not lend themselves to scheduling real-time applications, nor do they meet other scheduling requirements such as coordinating scheduling across several processors or machines, or enforcing isolation between applications, users, and administrative domains. Extending the scheduling subsystems of general-purpose operating systems in an ad hoc manner is time consuming and requires considerable expertise as well as source code to the operating system. Furthermore, once extended, the new scheduler may be as inflexible as the original.

The thesis of this dissertation is that extending a general-purpose operating system with a general, heterogeneous scheduling hierarchy is feasible and useful. A *hierarchy* of schedulers generalizes the role of CPU schedulers by allowing them to schedule other schedulers in addition to scheduling threads. A *general*, *heterogeneous* scheduling hierarchy is one that allows arbitrary (or nearly arbitrary) scheduling algorithms throughout the hierarchy. In contrast, most of the previous work on hierarchical scheduling has imposed restrictions on the schedulers used in part or all of the hierarchy.

This dissertation describes the Hierarchical Loadable Scheduler (HLS) architecture, which permits schedulers to be dynamically composed in the kernel of a general-purpose operating system. The most important characteristics of HLS, and the ones that distinguish it from previous work, are that it has demonstrated that a hierarchy of nearly arbitrary schedulers can be efficiently implemented in a general-purpose operating system, and that the behavior of a hierarchy of soft real-time schedulers can be reasoned about in order to provide guaranteed scheduling behavior to application threads. The flexibility afforded by HLS permits scheduling behavior to be tailored to meet complex requirements without encumbering users who have modest requirements with the performance and administrative costs of a complex scheduler.

Contributions of this dissertation include the following. (1) The design, prototype implementation, and performance evaluation of HLS in Windows 2000. (2) A system of *guarantees* for scheduler composition that permits reasoning about the scheduling behavior of a hierarchy of soft real-time schedulers. Guarantees assure users that application requirements can be met throughout the lifetime of the application, and also provide application developers with a model of CPU allocation to which they can program. (3) The design, implementation, and evaluation of two *augmented CPU reservation* schedulers, which provide increase scheduling predictability when low-level operating system activity *steals* time from applications.

# Acknowledgments

First of all, many thanks to my advisor Jack Stankovic for being supportive of me and my work, for giving me enough rope but not too much, for pushing me in the right direction when I was wasting time or missing the point, and for speedy turnaround on many iterations of each dissertation chapter during busy times.

I'd like to thank Mike Jones for introducing me to a relevant and interesting area of research, and for being a mentor as well as a de facto second advisor.

Thanks to my committee—Marty Humphrey, Mike Jones, Paul Reynolds, Sang Son, and Ron Williams—for useful advice and constructive criticism at the proposal, at my defense, and in between. I would also like to thank Paul for being the chair of my committee and for being a patient and supportive advisor during my first few years at UVA.

Thanks to David Coppit, Gabe Ferrer, Sean McCulloch, Mike Nahas, Anand Natrajan, Alastair Reid, Glenn Wasson, and Brian White for providing useful feedback on a draft of this dissertation. Special thanks to: Sean for going above and beyond the call of duty by reading something like five chapters in two days, Dave for applying the "Kevin standard" to my claimed contributions, Brian for curbing the excesses of my (sometimes overly) parenthetical writing style, Mike and Alastair for actually reading the proofs, and Nuts for making a massive contribution.

Thanks to Sarah Creem for her love, patience, and understanding.

I would like to thank my parents for always being supportive, and for advising without pushing. Also, thanks for providing me with the 1972 World Book Encyclopedia and a Texas Instruments 99/4a—I have no idea where I'd be if I hadn't had access to these things.

Thanks to SIGBEER and the Inner Circle—you know who you are—for being, in large part, responsible for making my stay at UVA an enjoyable one and for sustaining a level of Wrongness which, although occasionally excessive, was never unwarranted.

Thanks to Jay Lepreau and the rest of the Flux group at the University of Utah for helpful conversations and friendly advice, and for giving me space in their lab while I wrote this dissertation.

Finally, I would like to thank Ginny Hilton, Brenda Lynch, and Tammy Ramsey for giving me friendly help countless times over the past six years, and for providing a much-needed level of indirection between me and the University bureaucracy.

| Operating systems, in trying to meet the needs of applications, have to define what those needs are. Applications with different needs waste effort overcoming what is now a problem rather than a solution.  — Peter Williams, In Search of the Ideal Operating System for User Interfacing               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ideally, a general-purpose operating system that supports real-time execution should not a priori restrict the basic tenor of performance guarantees that any process is capable of obtaining.  — Ion Stoica et al., A Proportional Share Resource Allocation Algorithm for Real-Time, Time-Shared Systems |

| A schedule defends from chaos and whim.  — Annie Dillard, The Writing Life                                                                                                                                                                                                                                 |

# **Contents**

| 1 | Intr | oduction                                              | 1  |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | Motivation                                            | 1  |

|   | 1.2  | The Thesis                                            | 2  |

|   | 1.3  | Reasons to Use and Understand Hierarchical Scheduling | 3  |

|   | 1.4  | Overview of the HLS                                   | 4  |

|   | 1.5  | Scope of the Dissertation                             | 6  |

|   | 1.6  | Contributions                                         | 7  |

|   | 1.7  | Outline of the Dissertation                           | 8  |

| 2 | A St | rvey of Multimedia Programming Models                 | 9  |

|   | 2.1  | Introduction                                          | 9  |

|   | 2.2  | Multimedia System Requirements                        | 10 |

|   | 2.3  | Basis of a Taxonomy                                   | 11 |

|   | 2.4  | Applications Characterized                            | 20 |

|   | 2.5  | Challenges for Practical Soft Real-Time Scheduling    | 23 |

|   | 2.6  | Conclusions                                           | 23 |

| 3 | App  | lication Scenarios                                    | 24 |

|   | 3.1  | A Machine Providing Virtual Web Servers               | 24 |

|   | 3.2  | A Home Computer                                       | 25 |

|   | 3.3  | A Corporate or Departmental Terminal Server           | 26 |

|   | 3.4  | Coping with Inflexible Scheduling                     | 27 |

| 4 | Desi | gn of the Hierarchical Scheduler Infrastructure       | 29 |

|   | 4.1  | Goals and Requirements                                | 29 |

|   | 4.2  | Entities in the Scheduler Infrastructure              | 30 |

|   | 4.3  | The Loadable Scheduler Programming Model              | 30 |

|   | 4.4  | Scheduler Infrastructure Example                      | 41 |

|   | 4.5  | Conclusion                                            | 42 |

| 5 | Con  | posing Scheduling Policies                            | 43 |

|   | 5.1  | Guarantees                                            | 43 |

|   | 5.2  | Soft Real-Time Guarantees                             | 46 |

|   | 5.3  | Converting Between Guarantees                         | 51 |

|   | 5 4  |                                                       | 61 |

| Contents | viii |

|----------|------|

|----------|------|

| 6  | Issu | es and Examples for Scheduler Composition                   | 62  |

|----|------|-------------------------------------------------------------|-----|

|    | 6.1  | Guarantees for Multithreaded Applications                   | 62  |

|    | 6.2  | Synthesizing Complex Behaviors from Simple Schedulers       | 68  |

|    | 6.3  | Other Topics                                                | 73  |

|    | 6.4  | Conclusion                                                  | 76  |

| 7  | Sche | duling the Application Scenarios                            | 77  |

|    | 7.1  | A Machine Providing Virtual Web Servers                     | 77  |

|    | 7.2  | A Home Computer                                             | 78  |

|    | 7.3  | A Corporate or Departmental Terminal Server                 | 80  |

|    | 7.4  | Conclusions                                                 | 81  |

| 8  | The  | Resource Manager                                            | 82  |

|    | 8.1  | Introduction                                                | 82  |

|    | 8.2  | Entities in the Resource Manager                            | 83  |

|    | 8.3  | Guarantee Acquisition                                       | 84  |

|    | 8.4  | CPU Allocation Rules                                        | 85  |

|    | 8.5  | Supporting Unmodified Applications                          | 88  |

|    | 8.6  | Implementation                                              | 89  |

|    | 8.7  | Doing Without the Resource Manager                          | 89  |

|    | 8.8  | Conclusions                                                 | 90  |

| 9  | Imp  | lementation of HLS in a General-Purpose OS                  | 91  |

|    | 9.1  | Background and Implementation-Level Design Decisions        | 91  |

|    | 9.2  | Implementation of the Hierarchical Scheduler Infrastructure | 93  |

|    | 9.3  | Schedulers Implemented                                      | 97  |

|    | 9.4  | HLS Implementation Experience                               | 99  |

|    | 9.5  | •                                                           | 101 |

| 10 | Perf | ormance Evaluation of HLS                                   | 102 |

|    |      |                                                             | 102 |

|    |      | $\mathcal{E}_{\bullet}$                                     | 102 |

|    |      | Context Switch Times                                        |     |

|    |      | Overhead of High-Frequency Timer Interrupts                 |     |

|    |      |                                                             | 110 |

|    |      |                                                             | 114 |

|    |      |                                                             | 114 |

| 11 | Aug  | mented CPU Reservations                                     | 115 |

|    |      |                                                             | 115 |

|    |      |                                                             | 116 |

|    |      | •                                                           | 117 |

|    |      |                                                             | 117 |

|    |      |                                                             | 118 |

|    |      |                                                             | 120 |

|    |      | Other Criteria for Evaluating Rez-C and Rez-FB              | 124 |

| Contents | ix |

|----------|----|

|----------|----|

| C  | r r r r r r r r r r r r r r r r r r r               |    |

|----|-----------------------------------------------------|----|

|    | An Example Scheduler                                | 15 |

|    | B.4 Functions for Loading and Unloading a Scheduler | 15 |

|    | B.3 Constants, Variables, and Types                 | 15 |

|    | B.2 Functions Available to Schedulers               |    |

|    | B.1 Data Structures                                 | 1  |

| В  | The Loadable Scheduler Interface                    | 1  |

| A  | Glossary                                            | 1  |

|    | 13.2 Future Work                                    | 1  |

|    | 13.1 Summary of Contributions                       |    |

| 13 | Conclusions                                         | 1  |

|    | 12.2 Resource Management for the CPU                | 1  |

|    | 12.1 Hierarchical Scheduling                        | 1  |

| 12 | Related Work                                        | 1  |

|    | 11.10Conclusions                                    | 1  |

|    | 11.9 Other Approaches and Related Work              |    |

|    |                                                     |    |

# **List of Figures**

| High-level overview of the HLS architecture                                                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Relationship between schedulers and virtual processors                                           | 32<br>33<br>35<br>41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

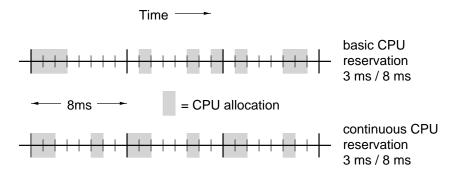

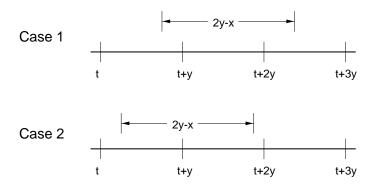

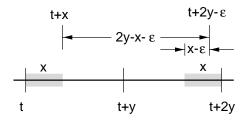

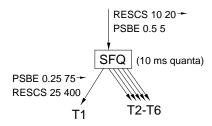

| Segment of a time-line showing when the CPU is allocated to a basic and a continuous reservation | 48<br>57<br>57<br>60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example of a per-application guarantee                                                           | 63<br>68<br>69<br>71<br>72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example scheduling hierarchy for a two-processor machine providing two virtual servers           | 78<br>79<br>80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pseudocode for a rule admitting the subset of applications that have the highest importance      | 86<br>87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

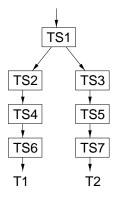

| Scheduling hierarchy used to measure the cost of a context switch involving 4 levels             | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

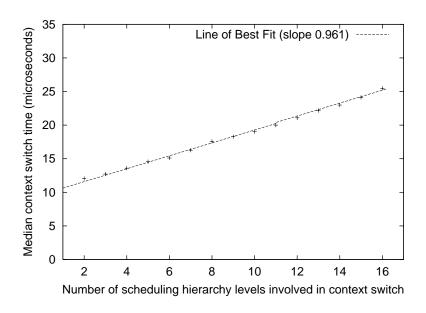

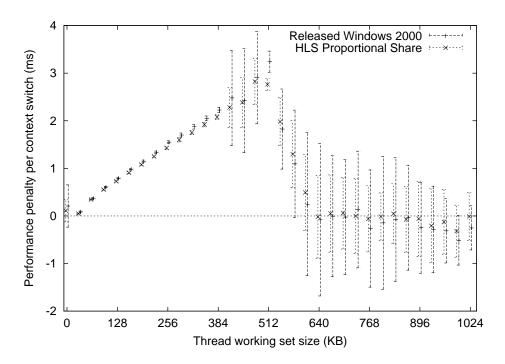

| Thread context switch time as a function of hierarchy depth                                      | 107<br>107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| does                                                                                             | <ul><li>110</li><li>113</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

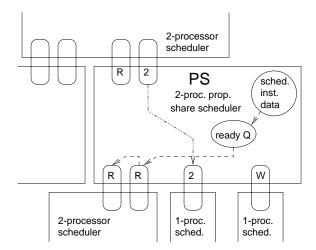

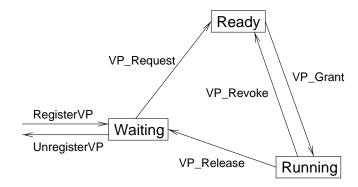

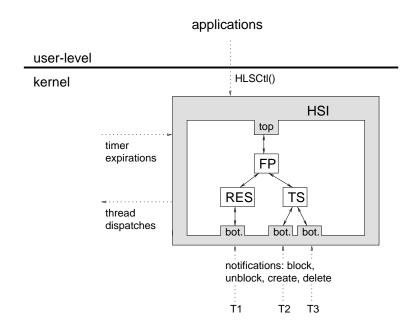

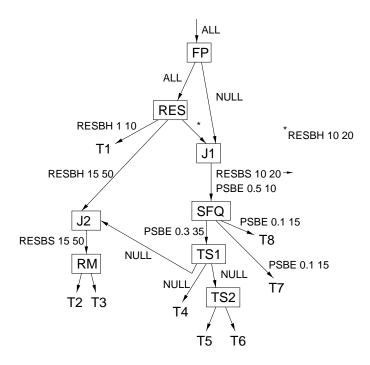

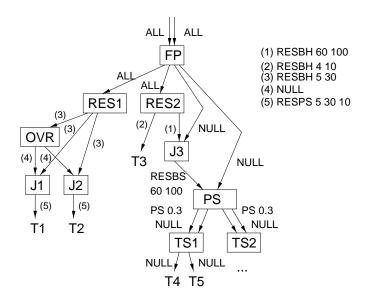

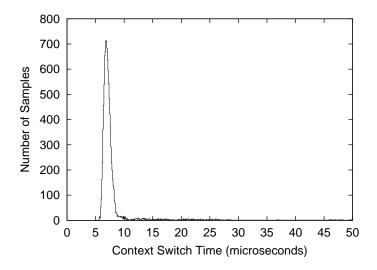

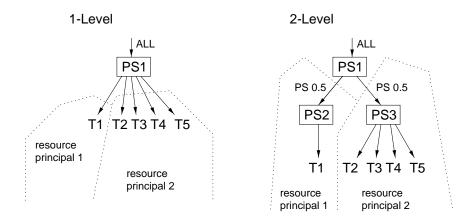

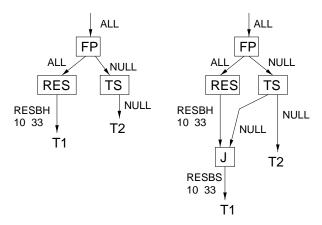

|                                                                                                  | Relationship between schedulers and virtual processors  Virtual processor state transition diagram  Detailed overview of the HSI  Scheduling hierarchy at the beginning of the example in Section 4.4  Segment of a time-line showing when the CPU is allocated to a basic and a continuous reservation  Time-lines for case analysis in the sufficient condition of the proof of Lemma 5.1  Time-line for the necessary condition of the proof of Lemma 5.1  Using an SFQ scheduler to provide a CPU reservation  Example of a per-application guarantee  Parameter space for a per-application CPU reservation  Scheduling hierarchy providing hard and soft reservations  Scheduling hierarchy providing probabilistic CPU reservations  A hierarchical implementation of Rialto  Example scheduling hierarchy for a two-processor machine providing two virtual servers  Example scheduling hierarchy for a home computer  Example scheduling hierarchy for a terminal server  Pseudocode for a rule admitting the subset of applications that have the highest importance  Pseudocode for a rule implementing fairness between users  Histogram of context switch times for the released Windows 2000 kernel  Scheduling hierarchy used to measure the cost of a context switch involving 4 levels of schedulers  Thread context switch time as a function of hierarchy depth  Thread performance penalty per context switch as a function of working set size  Thread performance penalty per context switch as a function of working set size  Scheduling hierarchies used to provide hard (left) and soft (right) CPU reservations |

List of Figures xi

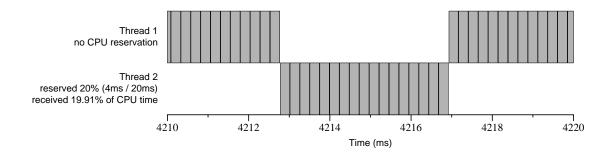

| 11.1 | Execution trace of a CPU reservation functioning correctly on an otherwise idle  |    |

|------|----------------------------------------------------------------------------------|----|

|      | machine                                                                          | 16 |

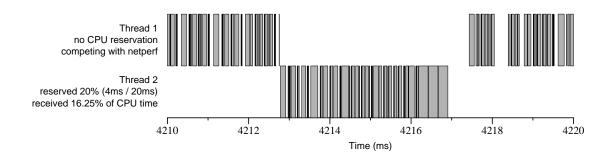

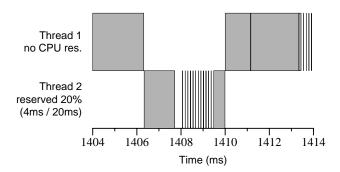

| 11.2 | Gaps in Thread 2's CPU time indicate time being stolen from a CPU reservation by |    |

|      | the kernel                                                                       | 16 |

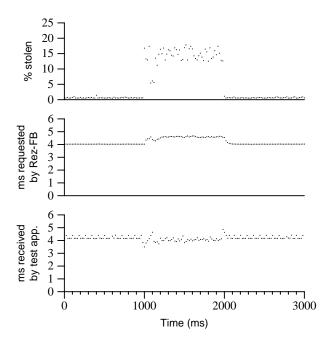

| 11.3 | Predictability of Rez, Rez-C, and Rez-FB                                         | 22 |

| 11.4 | Performance of Rez-FB under changing load                                        | 23 |

| 11.5 | Time stolen by the kernel to process an incoming TCP stream                      | 27 |

| 11.6 | Execution trace showing time stolen from a CPU reservation in Linux/RT by the    |    |

|      | IDE disk driver operating in PIO mode                                            | 28 |

| B.1  | Fields of the scheduler instance structure                                       | 17 |

| B.2  | Fields of the virtual processor structure                                        | 18 |

| B.3  | Fields of the scheduler callback structure                                       | 18 |

| B.4  | Functions provided to scheduler instances by the HSI                             | 5( |

# **List of Tables**

| 2.1<br>2.2 | Characterization of soft real-time schedulers                                                                                                                                                                                               | 12<br>20 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1<br>4.2 | Loadable scheduler entry points                                                                                                                                                                                                             | 31<br>35 |

| 5.1<br>5.2 | Guarantee conversions performed by schedulers                                                                                                                                                                                               | 51<br>56 |

| 6.1        | Requirements of threads in the Windows Media Player task set                                                                                                                                                                                | 67       |

| 9.1<br>9.2 | Mapping of Windows 2000 thread states to HLS virtual processor states Summary of changes to Windows 2000 to support hierarchical scheduling                                                                                                 | 93<br>96 |

| 10.2       | Time taken to perform representative HLS operations from user level Context switch times for HLS and native Windows 2000 schedulers Reduction in application throughput due to clock interrupts as a function of frequency and cache state. | 104      |

|            | Aggregate performance of isolated and non-isolated resource principals                                                                                                                                                                      | 111      |

| 11.1       | Amount of time stolen from a CPU reservation by disk device drivers                                                                                                                                                                         |          |

# Chapter 1

## Introduction

#### 1.1 Motivation

Complementary advances in storage, processing power, network bandwidth, and data compression techniques have enabled computers to run new kinds of applications, and to run combinations of applications that were previously infeasible. For example, a modern personal computer can simultaneously decode and display a high-quality video stream, encode an audio stream in real time, and accurately recognize continuous speech; any one of these would have been impossible on an inexpensive machine just a few years ago. Also, market pressure is encouraging vendors to migrate functionality previously performed in dedicated hardware onto the main processor; this includes real-time tasks such as sound mixing [39] and modem signal processing [41]. Furthermore, home and office networks, both wired and wireless, are making personal computers into attractive storage and processing servers for resource-limited networked devices such as stereos, digital still and video cameras, and personal digital assistants. In his keynote speech at COMDEX in January 2001 [7], Intel CEO Craig Barrett said that:

We have architected the latest generation of our microprocessor, the Pentium 4 processor, specifically for this. It was architected not to run [Microsoft] Word faster ... We did it to handle rich multimedia information. Whether it is for voice recognition, or animation or for gaming. Whether it is for showing video or capturing video or images.

Of course, powerful hardware alone is not enough—to reliably run combinations of real-time applications an operating system must effectively manage system resources such as processor time, storage bandwidth, and network bandwidth. Providing each resource to each task at an appropriate rate and granularity is no easy task; allocating at too high a rate or too fine a granularity is inefficient, and allocating at too low a rate or too coarse a granularity may reduce the value provided by applications. Scheduling is particularly difficult when the demand for one or more resources exceeds the supply—a situation that is all too common.

This dissertation focuses on the effective management of processor time, which is an important factor in overall system performance [66]. Traditional general-purpose operating systems (GPOSs) lack the flexibility required to support diverse workloads including multimedia and other soft real-time applications. They provide a single scheduling policy that is designed to support interactive and batch applications, and consequently they cannot provide application developers and users with meaningful guarantees about the level of service that applications will receive, and they cannot pro-

vide isolation between threads, applications, users, or other entities in the system. Furthermore, general-purpose operating systems give users very coarse controls for selectively allocating processor time to different applications, and they discourage potential implementors of innovative scheduling algorithms because their schedulers are interwoven with other operating system internals, and are therefore difficult to understand and modify.

#### 1.2 The Thesis

The thesis that this dissertation supports is:

Extending a general-purpose operating system with general, heterogeneous hierarchical CPU scheduling is feasible and useful.

A *hierarchy* of schedulers generalizes the role of CPU schedulers by allowing them to schedule other schedulers, as well as scheduling threads. A *general*, *heterogeneous* scheduling hierarchy is one that allows arbitrary (or nearly arbitrary) scheduling algorithms throughout the hierarchy. In contrast, most of the previous work on hierarchical scheduling has imposed restrictions on the schedulers used in part or all of the hierarchy. This dissertation describes the Hierarchical Loadable Scheduler (HLS) architecture, which permits schedulers to be dynamically loaded into the kernel of a general-purpose operating system.

The feasibility of general, heterogeneous hierarchical scheduling is demonstrated by (1) the design, implementation, and performance evaluation of the hierarchical scheduler infrastructure (HSI) in combination with several loadable schedulers and (2) the design of a system of *guarantees* for reasoning about the ongoing allocation of CPU time to soft real-time threads. The most important characteristics of HLS, and the ones that distinguish it from all previous work, are (1) that it has demonstrated that general, heterogeneous hierarchical scheduling can be efficiently supported by the kernel of a general-purpose operating system and that (2) the scheduling behavior of a general, heterogeneous hierarchy of soft real-time schedulers can be reasoned about in order to provide guaranteed scheduling behavior to application threads.

The usefulness of HLS is supported by showing that many deficiencies of the schedulers in general-purpose operating systems can be solved in a flexible way using a dynamically loaded hierarchy of schedulers. In particular, applications with diverse requirements can be supported by loading schedulers or combinations of schedulers that provide appropriate and, in some cases, guaranteed scheduling behavior. Guarantees provide the developers of real-time applications with a model of CPU allocation to which they can program. Guarantees also benefit end users by providing a mechanism for ensuring that the scheduling requirements of an important application will be met for the duration of the application's execution, or at least until the user wants the guarantee to end. Finally, the scheduling hierarchy supports multi-level isolation between threads, applications, and other entities.

The advantage of a flexible scheduling hierarchy over a *monolithic*, or fixed, scheduling policy is that it allows the complexity of the scheduler to be tailored to different situations. For example, a single user machine that runs a few undemanding multimedia applications can use a very simple scheduling hierarchy—the user is not forced to pay the administrative and run-time costs associated with complex scheduling behavior. Similarly, a powerful machine that must isolate the CPU usage of different users from each other while supporting multiple real-time applications can employ a

much more sophisticated scheduling hierarchy—in this case users can expect their real-time applications to work (if the machine has sufficient capacity to run them) and they will not be forced to deal with unfairness issues that can result from lack of isolation. In short, we assert that there is no good "one size fits all" scheduler for general-purpose operating systems.

Additional benefits of HLS include a well-defined programming interface that can reduce the effort associated with implementing new schedulers. This is accomplished by providing loadable schedulers with the notifications about operating system events that they require in order to make scheduling decisions, while abstracting away operating-system-specific details that do not concern the scheduler. Finally, a rule-based resource manager can be used in conjunction with the scheduling hierarchy to map application threads to appropriate schedulers based on their requirements, and to enforce high-level user- and administrator-supplied policies about the allocation of processor time.

## 1.3 Reasons to Use and Understand Hierarchical Scheduling

The flexibility enabled by hierarchical CPU scheduling has a number of advantages:

- Variety Multimedia applications have diverse requirements. HLS allows applications to be matched with schedulers that provide the real-time scheduling properties that they require.

- Isolation Generalizing the role of schedulers by allowing them to schedule other schedulers allows isolation properties (such as a guaranteed share of the CPU) to be recursively applied to groups of threads, rather than applying only to single threads.

- Decomposition HLS allows complex composite scheduling behaviors to be expressed as a collection of small, simple schedulers, providing increased flexibility compared to the "one size fits all" approach of monolithic schedulers.

- Experimentation HLS facilitates rapid prototyping of new schedulers by allowing a new scheduler to schedule only a subset of the threads on a machine rather than taking over the job of scheduling all threads. It also permits iterations of a scheduler to be tested without rebooting the operating system.

Even in situations where it is undesirable to place an explicit scheduling hierarchy in an operating system kernel, it is useful to understand the properties of hierarchical schedulers because there are many real-world cases of *implicit hierarchical scheduling*. For example, the kernel thread scheduler in a general-purpose operating system in combination with the scheduler for a user-level thread package, the scheduler for threads in a Java virtual machine, or the kernel thread scheduler for an operating system being run in a virtual machine such as VMWare, forms a hierarchical scheduler. The kernel scheduler itself in a general-purpose operating system can be viewed as a hierarchical scheduler: a fixed-priority scheduler implemented in hardware schedules interrupts at the highest overall priority, a (usually) FIFO scheduler runs low-level kernel tasks at the middle priority, and application threads are run at the lowest priority using what is usually thought of as "the scheduler." Furthermore, when the co-resident operating system approach to real-time is used [11,93], the kernel scheduler for a general-purpose OS is no longer the root scheduler; this privilege is taken over by a small hard-real-time OS.

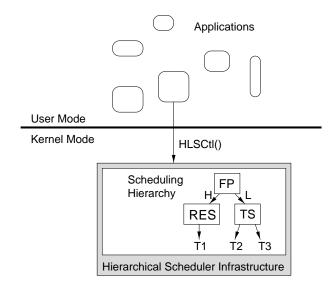

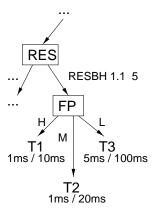

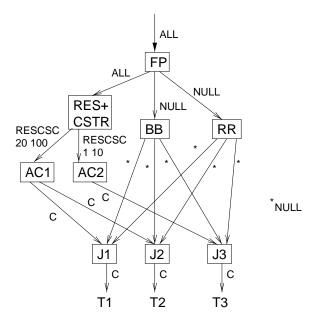

Figure 1.1: High-level overview of the HLS architecture

#### 1.4 Overview of the HLS

Conventional time-sharing scheduling algorithms are designed with a set of tradeoffs in mind; applications running under these schedulers are forced to cope with these tradeoffs. Since general-purpose operating systems are used in diverse ways, sometimes unanticipated by the designers of the OS, it is difficult to select, in advance, the right scheduler for an operating system. A premise of HLS is that scheduling algorithms should not be chosen in advance by operating system designers. Rather, scheduling policies and combinations of scheduling policies implementing desired behaviors should be dynamically loaded into the operating system to meet the scheduling requirements of a particular usage scenario.

#### 1.4.1 Systems Architecture

Figure 1.1 depicts the HLS architecture. The scheduling hierarchy is implemented in the kernel of a general-purpose operating system, where it is supported by the hierarchical scheduler infrastructure. There is a *root* scheduler at the top of the hierarchy that controls the allocation of all processor time. It grants the CPU to its *children*, which are below it in the hierarchy. The children may further subdivide processor time to their children, until a *leaf* of the hierarchy is reached; leaves always represent threads.

In Figure 1.1 FP, a fixed priority scheduler, is the root and RES and TS are its children. RES is a real-time scheduler and TS is a time-sharing scheduler. FP runs RES at a higher priority than TS—this means that any time RES is able to run, it is guaranteed to have access to a processor, allowing it to make real-time guarantees. It is not the case that TS can always get access to a processor: since it is scheduled at a lower priority than RES, it simply does not get to schedule any threads while RES is running. RES has one thread to schedule, T1, while TS is scheduling two threads, T2 and T3.

A request for a certain type of scheduling behavior is made by contacting the scheduling hierarchy using the HLSCtl command. Applications may make requests on their own, or a middleware resource manager may make requests on their behalf. If a resource manager is being used, it can also ensure that a particular request does not violate any user- or administrator-supplied rules about the allocation of CPU time.

#### 1.4.2 Architecture over Time

It is important to understand the three distinct time scales over which the scheduling hierarchy interacts with applications and users.

Long: The longest-term decision that needs to be made to use HLS concerns the way a particular computer will be used—this will determine the initial shape of the scheduling hierarchy. For example, basic time-sharing usage of a personal computer requires only a single scheduler. On the other hand, providing load isolation between users while supporting multiple real-time applications with different kinds of requirements may necessitate a complex hierarchy. For a given initial hierarchy, variations in usage can be accommodated by adding, deleting, or changing parts of the hierarchy. For example, a user might at first require only time-sharing behavior, but later want to isolate the CPU usage of an untrusted application. This can be accomplished by creating a new scheduler that is a child of the main time-sharing scheduler to run threads belonging to the untrusted application. The scheduler composition logic described in Chapter 5 describes how hierarchical collections of schedulers can be shown to provide correct real-time behavior.

**Medium:** At the medium time scale the scheduling hierarchy remains constant while applications are instantiated, exit, and change their requirements. Decisions at this level are expected to last for seconds or minutes, and possibly for much longer. New applications are assigned scheduling from a *default* scheduler; they may then request other kinds of scheduling, or other kinds of scheduling may be requested on their behalf. The actual decision of whether a particular scheduler can grant a particular request for scheduling is made by the scheduler itself, using a *schedulability analysis* routine. For example, a voice recognition application could request an ongoing share of 10% of the CPU by sending a message to the appropriate scheduler. The return value of the message would indicate that either yes, the scheduler has enough spare capacity to reserve 10% of the processor, or no, it does not, in which case the user could manually reduce system load or try to run the application later.

**Short:** At the short time scale, the scheduling hierarchy and the set of applications and their requirements remain constant. This is the level at which individual scheduling decisions are made by schedulers in the hierarchy, on a granularity of milliseconds or tens of milliseconds. For example, at this level a scheduler that has guaranteed a real-time thread to receive at least 3 ms of CPU time during every 50 ms interval would use a timer to have the Hierarchical Scheduler Infrastructure send it a notification every 50 ms so that it could schedule the thread.

These time scales are intended to be descriptive of the ways that computers running general-purpose operating systems are often used, rather than being prescriptive, or telling users how to use HLS. For example, there is nothing stopping an application from requesting a different guarantee ten times per millisecond, and in fact, the entire scheduling hierarchy on a machine can be reconfigured quite rapidly. Still, it is expected that the *core scheduling hierarchy* on a machine will remain stable for a considerable length of time, often for at least for the length of time between reboots. This

reflects the basic insight that most computers are purchased and used for some purpose, even if that purpose is a very general one like "running interactive and multimedia applications."

General-purpose operating systems with traditional time-sharing schedulers lack flexibility over long time scales since they have a single, fixed scheduling policy. They have some flexibility at medium time scales, but in most cases it is limited to changing the priorities of threads and limiting threads to run on a subset of the processors on a multiprocessor machine.

## 1.5 Scope of the Dissertation

Multimedia scheduling is a broad topic. In order to limit the scope of this dissertation a number of assumptions have been made. This section lists them and provides brief discussion and justification.

- HLS is designed to run in a general-purpose operating system. Virtually all personal computers and workstations run a GPOS. People use them to run multimedia applications, traditional interactive applications, background applications, and non-interactive server applications. GPOSs have been tailored to support non-real-time applications over the past several decades, and they support these applications well. It is unlikely that operating systems designed primarily to support real-time applications will replace GPOSs despite the increasing importance of multimedia and other soft real-time applications.

- Only scheduling the CPU. Resources other than the CPU such as memory, disk bandwidth, and network bandwidth can play an important role in overall application performance. However, while CPU scheduling is useful on its own (many applications do not require significant disk or network bandwidth), neither disk nor network bandwidth is useful without being accompanied by processor cycles to use the data. Furthermore, network quality of service is a separate topic and a large research area on its own.

- Not attempting to make a GPOS into a real-time OS. HLS defines an architecture for adding support for flexible scheduling to a general-purpose operating system. However, loading a real-time scheduler into a GPOS does not turn it into a real-time OS. In fact, general-purpose operating systems cannot, in general, be expected to reliably schedule real-time tasks that have sub-millisecond deadlines. However, ongoing improvements to GPOSs are being driven by the increasing importance of multimedia applications. For example, there are "low-latency" patches for Linux that reduce observed worst-case scheduling latency from tens or hundreds of milliseconds to less than 5 ms. Similarly, by avoiding hardware whose drivers are known to introduce scheduling delays, Windows 2000 can be used to attain reliable millisecond-granularity scheduling [38].

- Applications are soft real-time, and have deadlines of at least millisecond granularity. This assumption matches the requirements of most multimedia applications. They are soft real-time in the sense that missing a deadline is usually not catastrophic. Real-time requirements for multimedia generally come from users, who want to see a certain frame rate, reliably play stored sound files, etc. Due to the limited speed of human perceptual processing, these deadlines are usually in the 10–100 ms range.

- Application resource requirements are known, or can be determined. Real-time scheduling techniques rely on having an accurate estimate, for each task, of the amount of CPU time that is required and the time by which it must be received.

- *Hierarchical schedulers are trusted.* Schedulers, like other loadable device drivers, are assumed to be bug-free and to not contain malicious code. Trusting schedulers allows the entire hierarchy to be written in C and to execute in the kernel address space.

#### 1.6 Contributions

The contributions of this dissertation fall into five categories.

**Programming models:** The *programming model* is identified as an important aspect of supporting multimedia applications in general-purpose operating systems. A taxonomy of multimedia programming models is presented: the first-order distinction made by the taxonomy is between the scheduling algorithms used to multiplex processor time on short time scales (milliseconds or tens of milliseconds) and the high-level mode-change protocols used to allocate CPU time over longer time periods (seconds, minutes, or longer).

Scheduler composition: The underlying unity of the scheduling behaviors provided by a broad class of multimedia scheduling algorithms is exploited in order to develop a novel system of formal guarantees about the way that schedulers allocate CPU time. This system is useful because: it separates abstract scheduling behaviors from the algorithms that provide them, it shows which guarantees are equivalent to which other guarantees, and it allows the scheduling behavior of a hierarchy of schedulers to be reasoned about. Also, a new result about the schedulability of a task set using a rate monotonic scheduler that is given a CPU reservation is presented. Finally, it is demonstrated that a number of complex, idiomatic scheduling behaviors that have been described in the literature can be implemented using HLS schedulers as basic components.

Hierarchical scheduler infrastructure: The design, implementation, and performance evaluation of an architecture supporting a hierarchy of schedulers in the kernel of a multiprocessor operating system is presented. The scheduler infrastructure is based on a novel extension of the virtual processor abstraction that was developed for *scheduler activations* [3]. It is also novel in that it is the first system that permits a hierarchy of generic scheduling algorithms to be dynamically loaded into the kernel of a general-purpose operating system. The scheduler infrastructure facilitates the implementation of new schedulers by providing a simplified programming model: it isolates loadable schedulers from OS complexities such as extraneous thread states and a difficult multiprocessor programming model. Operations on the scheduling hierarchy such as creating or destroying a scheduler instance, moving a thread between schedulers, and beginning or ending a CPU reservation can be performed quickly: they all take less than  $40\,\mu s$  on a 500 MHz Pentium III. Finally, although HLS increases the cost of a context switch slightly, we show that the performance penalty that a context switch imparts to a thread in terms of re-establishing its working set in the processor cache can easily be two orders of magnitude greater than the cost added by HLS.

**Resource manager:** The high-level design (but not detailed design or implementation) of a rule-based, user-level *resource manager* is presented. The novel feature of the resource manager is that it makes use of reflective information about the scheduling hierarchy, as well as information about users and applications, in order to implement high-level policies about the allocation of CPU time.

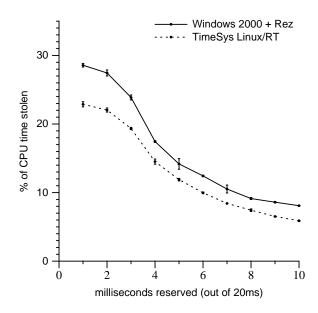

**Augmented CPU reservations:** *Stolen time* is defined and shown to be a potential obstacle to the predictable execution of real-time applications on general-purpose operating systems. For example, on a 500 MHz Pentium III running Windows 2000 more than 25% of a CPU reservation's time can be stolen by the network stack. On the same machine running Linux, close to 50% of a CPU reservation's time can be stolen by the IDE disk driver.

Two novel scheduling algorithms, Rez-C and Rez-FB, that provide *augmented CPU reservations* were designed, implemented, and evaluated. Augmented CPU reservations provide applications with increased predictability in the presence of stolen time. For example, a test application scheduled by Rez (which does not provide augmented reservations) must over-reserve by almost 25% to avoid missing deadlines when the network stack steals time from it. When scheduled by Rez-C or Rez-FB, 6% over-reservation is sufficient to eliminate nearly all deadline misses.

### 1.7 Outline of the Dissertation

Chapter 2 provides additional motivation for HLS by examining the relationship between the programming models that are provided by important classes of soft real-time schedulers, the properties of multimedia applications, and the conflicting requirements that must be satisfied by a generalpurpose operating system that also supports multimedia applications. Chapter 3 describes three application scenarios that motivate support for flexible scheduling in general-purpose operating systems. Chapter 4 presents the design of the Hierarchical Scheduler Infrastructure (HSI)—the in-kernel component of HLS that supports loadable schedulers. In Chapter 5 the guarantee system for verifying the composability of hierarchical multimedia schedulers is presented. Chapter 6 continues the subject of scheduler composition, and includes a section showing that complex and useful scheduling behaviors can be composed using simple schedulers as components. Solutions to the scheduling challenges posed by the application scenarios in Chapter 3 are presented in Chapter 7. The design of the HLS resource manager is presented in Chapter 8. Chapter 9 describes the issues involved with implementing the HSI in the Windows 2000 kernel. Chapter 10 presents data about the performance of the prototype implementation. Chapter 11 describes and evaluates two schedulers that can increase predictability for applications executing on general-purpose operating systems in the presence of stolen time. Chapter 12 compares elements of the HLS architecture with related work that has appeared in the literature. Conclusions and future work are presented in Chapter 13. Finally, Appendix A contains an alphabetical list of technical terminology used in this dissertation, Appendix B describes the programming interface for loadable schedulers, and Appendix C contains source code for a loadable scheduler.

# **Chapter 2**

# A Survey of Multimedia Programming Models

This chapter presents background and motivation for the HLS architecture. It analyzes operating system support for soft real-time applications in terms of the different classes of schedulers that have been described in the literature and their associated programming models. Also, the requirements of several common types of multimedia applications are described in order to understand how applications can be matched with appropriate schedulers.

#### 2.1 Introduction

The set of abstractions and conventions implemented by a particular system that allow soft real-time applications to meet their requirements defines a *programming model*. A multimedia scheduler must support a programming model that is useful and understandable to the people who develop applications for the system. Furthermore, the scheduler, in conjunction with applications, must meet user expectations and provide understandable behavior in the face of sets of applications that demand resources exceeding the capacity of the system.

For example, SMART [67] and Rialto [40] both offer deadline-based scheduling to applications in the form of *time constraints*. To use a time constraint, an application requests an amount of CPU time before a deadline (for example, 20 ms of processing during the next 100 ms); the scheduler then notifies the application that the constraint is either accepted or rejected.

Although both systems provide the same basic abstraction, the guarantees they offer are different. Once Rialto informs an application that a requested time constraint is feasible it guarantees that the time for that constraint will have been dedicated to the requesting application no matter what other applications might do. SMART, on the other hand, may invalidate a previously accepted time constraint part way through its execution, taking away its reserved time, if a higher-priority application requests a conflicting time constraint. So, SMART potentially provides faster response time for higher-priority applications that unexpectedly request CPU time, but Rialto supports a programming model in which a developer does not need to worry about the case in which a feasible time constraint is not actually scheduled.

In both cases the designers of the system believed they were making the right decision. How can it be that one man's features are another man's bugs? Clearly the authors have not agreed upon either the goals they were trying to achieve or the criteria by which their systems should be

judged. Tradeoffs such as the one in this example are important because they affect the basic set of assumptions that programmers can make while implementing multimedia applications.

This chapter analyzes the sets of goals that multimedia schedulers might try to achieve. It creates a taxonomy of the kinds of programming models used to achieve these goals and it characterizes a number of representative systems used to run multimedia applications within this taxonomy. The top-level distinction made by this taxonomy is between high-level algorithms used to respond to changes in application requirements, and low-level algorithms used to make individual scheduling decisions. For each of these two broad classes we present a number of sub-categories, including representative algorithms and their important properties.

The use of this taxonomy is intended to enable: (1) careful comparisons to be made between existing work, (2) the identification of new parts of the design space leading to possible new solutions, and (3) a better understanding of how the needs of several types of multimedia applications are served by (or are not well-served by) the various programming models promoted by important types of multimedia schedulers.

# 2.2 Multimedia System Requirements

### 2.2.1 Context for the Requirements

A *general-purpose operating system* (GPOS) for a PC or workstation must provide fast response time for interactive applications, high throughput for batch applications, and some amount of fairness between applications. Although there is tension between these requirements, the lack of meaningful changes to the design of time-sharing schedulers in recent years would seem to indicate that they are working well enough.

The goal of a hard real-time system is similarly unambiguous: all hard deadlines must be met. The design of the system is dictated by this requirement, although it conflicts to some extent with designing a low-cost system. Despite the conflict, there appears to be a standard engineering practice for building such systems: statically determine resource requirements and then overprovision processor cycles as a hedge against unforeseen situations.

Not surprisingly, there is a large space of systems whose requirements fall between these two extremes. These are soft real-time systems: they need to support a dynamic mix of applications, some of which must perform computations at specific times. Missed deadlines are undesirable, but not catastrophic. In this chapter we are concerned with the requirements placed upon general-purpose operating systems that have been extended with soft real-time schedulers for the purpose of supporting multimedia applications.

We have attempted to identify an uncontroversial set of requirements that the "ideal" multimedia operating system would meet. We do not claim that the HLS architecture can meet all of these requirements, and in fact, it is unlikely that any single system can meet all of these requirements for all types of applications. Even so, the requirements are important because they describe the space within which multimedia systems are designed. A particular set of prioritizations among the requirements will result in a specific set of tradeoffs, and these tradeoffs will constrain the design of the user interface and the application programming model of a system.

### 2.2.2 List of Requirements

**R1:** *Meet the scheduling requirements of coexisting, independently written, possibly misbehaving soft real-time applications.*

The CPU requirements of a real-time application are often specified in terms of an *amount* and *period*, where the application must receive the amount of CPU time during each period of time. No matter how scheduling requirements are specified, the scheduler must be able to meet them without the benefit of global coordination among application developers—multimedia operating systems are *open systems* in the sense that applications are written independently.

A misbehaving application (from the point of view of the scheduler) will *overrun* by attempting to use more CPU time than was allocated to it. Schedulers that provide *load isolation* guarantee a minimum amount or proportion of CPU time to each multimedia application even if other applications overrun (by entering an infinite loop, for example).

**R2:** *Minimize development effort by providing abstractions and guarantees that are a good match for applications' requirements.*

An important role of the designers of soft real-time systems is to ease application developers into a world where their application gracefully shares machine resources with other applications. We propose the following test: compare the difficulty of writing an application for a given multimedia scheduler to the difficulty of writing the same application if it could assume that it is the highest priority application in the system (thus having the machine logically to itself). If the difference in costs is too high, application developers will assume that contention does not exist. Rather than using features provided by the scheduler, they will force their users to manually eliminate contention.

Getting the programming model right is very important: if a system becomes widely used, the effort expended by application developers will far outweigh the effort required to implement the system. It is therefore possible for small increases in usability to justify even large amounts of implementation complexity and effort. In other words, the programming model matters.

**R3:** *Provide a consistent, intuitive user interface.*

Users should be able to easily express their preferences to the system and the system should behave predictably in response to user actions. Also, it should give the user (or software operating on the user's behalf) feedback about the resource usage of existing applications and, when applicable, the likely effects of future actions.

**R4:** Run a mix of applications that maximizes overall value.

Unlike hard real-time systems, PCs and workstations cannot overprovision the CPU resource; demanding multimedia applications tend to use all available cycles. The multimedia OS should avoid conservatively rejecting applications that may be feasible. During overload, the multimedia OS should run a mix of applications that maximizes overall value. Value is a subjective measure of the utility of an application, running at a particular time, to a particular user.

# 2.3 Basis of a Taxonomy

The top level of our taxonomy of scheduling support for multimedia applications makes a distinction between low-level algorithms that make individual scheduling decisions, and higher-level algorithms that respond to application mode changes (when an application starts, terminates, or has a change of requirements). The second level of the taxonomy breaks these broad categories into

| programming model       | examples                  | mples load prior |                   | support for varying   |

|-------------------------|---------------------------|------------------|-------------------|-----------------------|

|                         |                           | isolation        |                   | latency requirements? |

| rate-monotonic and      | Linux, RTLinux, Solaris,  | isolated from    | period, amount    | yes                   |

| other static priority   | Windows 2000              | lower priority   |                   |                       |

| CPU reservations        | Nemesis, Rialto, Spring   | strong           | period, amount    | yes                   |

| proportional share      | BVT, EEVDF, SMART         | strong           | share (, latency) | varies                |

| earliest deadline first | Rialto, SMART             | strong / weak    | amount, deadline  | yes                   |

| feedback control        | FC-EDF, SWiFT             | varies           | metric, set point | varies                |

| hierarchical scheduling | CPU Inheritance, SFQ, HLS | varies           | varies            | varies                |

Table 2.1: Characterization of soft real-time schedulers

classes of algorithms such as "CPU reservations" and "admission-control." We identify important features of these classes and place representative schedulers from the literature within them. The key questions that we answer about each category is:

- What information must applications provide to the system with in order to benefit from the scheduler?

- What kinds of guarantees are made to applications?

- What kinds of applications are supported well (and poorly)?

- Whose jobs does it make easier (and harder)?

- How comprehensible and usable is the resulting programming interface?

- How comprehensible and usable is the resulting user interface?

#### 2.3.1 Steady State Allocation of CPU Time

For each scheduler, we provide a brief description, give examples of systems that implement it, and examine which of the requirements from Section 2.2 the scheduler fulfills. These characteristics are summarized in Table 2.1.

#### 2.3.1.1 Static Priority and Rate Monotonic Scheduling

The uniprocessor real-time scheduling problem has essentially been solved by *static priority analy-sis* [4] when the set of applications and their periods and amounts are known in advance, and when applications can be trusted not to overrun. Static priority schedulers maintain the simple invariant that the runnable thread with highest priority is always scheduled. Static-priority scheduling is a generalization of *rate monotonic analysis* [53]. The core result of rate monotonic analysis is that if a set of independent periodic tasks is scheduled rate monotonically—with the shortest-period task having the highest priority, the second-shortest having the second-highest priority, and so on—then no task will ever miss a deadline as long as the total utilization over all tasks is less than 69%.

Popular general-purpose operating systems such as Linux and Windows 2000 extend their timesharing schedulers to support static priority threads that have strictly higher priority than any timesharing thread. Schedulers with this structure exhibit well-known pathologies such as unbounded priority inversion (unless synchronization primitives have been augmented to support priority inheritance) and starvation of time-sharing applications during overload [66]. Furthermore, developers are likely to overestimate the priority at which their applications should run because a poorly performing application reflects negatively on its author. This phenomenon is known as *priority inflation*.

BeOS has a clever requirement that, if followed, will not only eliminate priority inflation but also achieve an approximate rate-monotonic schedule: static priorities are explicitly tied to thread latency requirements, with higher priorities corresponding to shorter latencies. For example, programmers are encouraged to schedule threads with a 5–10 ms latency sensitivity at priority 110, and threads with a 0.5–1 ms latency sensitivity at priority 120 [60].

Although static priority schedulers are simple, efficient, and well understood, they fail to isolate applications from one another, and optimal priority assignment requires coordination among application developers. Applications can only be guaranteed to receive a certain amount of CPU time if the worst-case execution times of higher-priority applications are known, and this is generally not possible. Still, the static-priority programming model is reasonably intuitive for both users (if an application is starving, there must be overload at higher priorities) and programmers (higher priority applications run first), and it supports legacy applications.

#### 2.3.1.2 CPU Reservations